Процесор AMD Ryzen X3D / ITC.UA

Ще на початку 2021 року з’явилися перші чутки про новий тип кеш-пам’яті, над яким працювала AMD. Остаточно компанія представила цю технологію в середині року на Computex 2021, давши їй назву 3D V-Cache. Йдеться про вертикально скомпонований кеш останнього рівня, який дозволяє розмістити значно більший обсяг пам’яті на мінімальній площі кристала.

Наразі AMD використовує друге покоління 3D V-Cache, а на виставці CES 2026 компанія представила процесор Ryzen 7 9850X3D, який назвала найшвидшим ігровим процесором у світі.

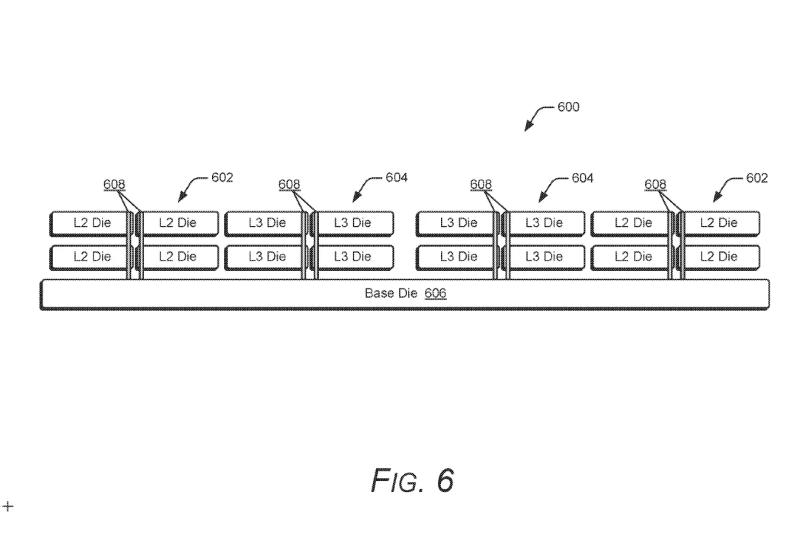

В архітектурі Zen кеш останнього рівня відповідає L3, однак новий патент свідчить, що AMD вирішила піти далі й звернути увагу на L2-кеш. Документ вказує, що компанія експериментує з вертикальним стекуванням кешу другого рівня, щоб отримати ще вищу продуктивність і кращу енергоефективність у майбутніх процесорах Ryzen X3D.

AMD подала патент на технологію під назвою Balanced Latency Stacked Cache. Ця конструкція спрямована на зменшення затримок доступу до кеш-пам’яті та подальше зниження енергоспоживання. У порівнянні з класичними процесорами без 3D-кешу, планарні рішення мають вищі затримки та більші енергетичні витрати, що безпосередньо впливає на швидкодію й ефективність.

Згідно з описом патенту, новий дизайн 3D L2-кешу дозволяє зменшити затримку доступу до стандартного L2-кешу обсягом 1 МБ з 14 тактів до 12 тактів. На перший погляд, різниця здається незначною, однак у проєктуванні процесорів навіть кілька зекономлених тактів суттєво впливають на кінцеву продуктивність і енергоефективність. Для розуміння масштабу: типовий L2-кеш має затримку в діапазоні 10–50 тактів, тож заявлені показники виглядають дуже конкурентно.

Хочеш знати більше, ніж ChatGPT 5? Підписуйся на ITC.ua у TelegramПІДПИСАТИСЯ

Патент також пояснює технічну реалізацію. Стековані кристали з’єднуються за допомогою наскрізних кремнієвих з’єднань (TSV) або контактних переходів (BPV) для вертикального обміну даними між шарами. Ці з’єднання проходять через центральну частину кристалів, що скорочує довжину сигнальних шляхів. Такий підхід формує симетричну, збалансовану структуру, яка забезпечує однаковий час доступу до даних на всіх рівнях кешу. Саме цим і пояснюється назва Balanced Latency Stacked Cache.

Водночас патент поки перебуває на стадії розгляду. Сам факт його подачі не гарантує появу технології в серійних продуктах. Теоретичні розрахунки не завжди повністю відтворюються в реальних процесорах, тож остаточні результати залежатимуть від практичної реалізації.

СпецпроєктиWi-Fi 7: топ-5 роутерів від TP‑Link для різних завдань та поради, як обрати свій варіантГоловні тренди 2026-го у відеоспостереженні – від ШІ-обробки до звуку. Розбираємо з експертами VIATEC